## SONY

# CXP5076/5078

## **CMOS 4-bit Single Chip Microcomputer**

## Description

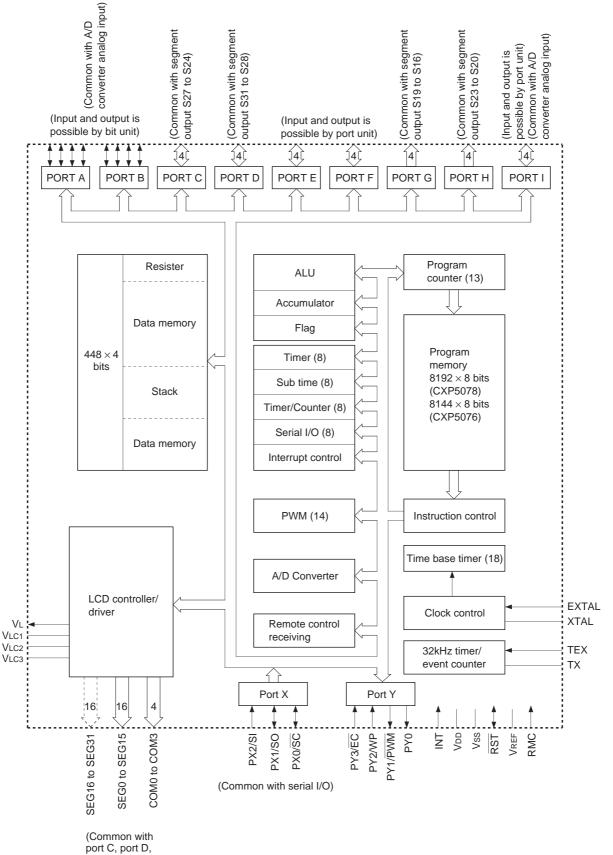

CXP5076/5078 is a CMOS 4-bit microcomputer which consists of 4-bit CPU, ROM, RAM, I/O port, 8-bit timer, 8-bit timer/counter, 18-bit time base timer, 8-bit serial I/O, vector interruption, power on reset function, liquid crystal displayer (LCD) controller/driver, D/A conversion 14-bit PWM output port, a remote control reception circuit with noise eliminating circuit, 3-bit A/D converters, a 32kHz timer/event counter and a power supply voltage detection reset function. They are integrated into a single chip with the standby function, etc. which are to be operated at a low power consumption.

## Features

- Instruction cycle 1.9

- 1.9μs/4.19MHz 122 μs/32kHz

(Possible to select with the program)

- ROM capacity

- 8192 × 8 bits (CXP5078) 6144 × 8 bits (CXP5076)

- RAM capacity 448 × 4 bits (Including stack, display area)

- 43 general purpose I/O ports

- 8 high current output ports

- LCD controller/driver (Possible to direct drive)

- Possible to select with the program the segment output of 16 to 32

- Possible to select with the program the duty of static, 1/2, 1/3 and 1/4

- Possible to select with the program the bias of 1/2, 1/3

- 14-bit PWM output for D/A conversion

- Remote control reception circuit

- 3-bit A/D converter (8 channels per circuit)

- 32kHz timer/event counter

- Power supply voltage detection reset function

- Low voltage operation (2.5V) ..... when operating in 122µs/32kHz

- Rich wake-up function

- 8-bit/4-bit variable serial I/O

- Arithmetic and logical operations possible between the entire ROM area, I/O area and the accumulator by means of the memory mapped I/O

- 8-bit timer, 8-bit timer/event counter and 18-bit time base timer, independently controlled

- 2 kinds of power down modes of sleep and stop

- Power on reset circuit (mask option)

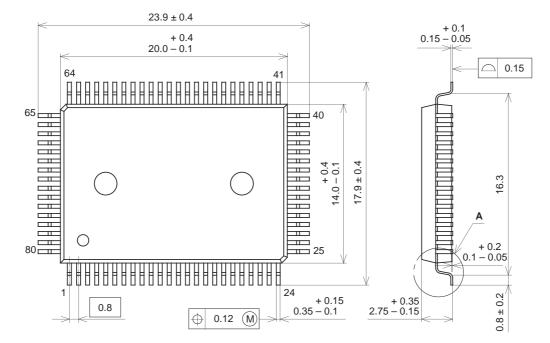

- Provided with 80 pin plastic QFP

- Provided with 80 pin piggyback QFP (CXP5070)

## Structure

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

#### **Block Diagram**

port G, port H)

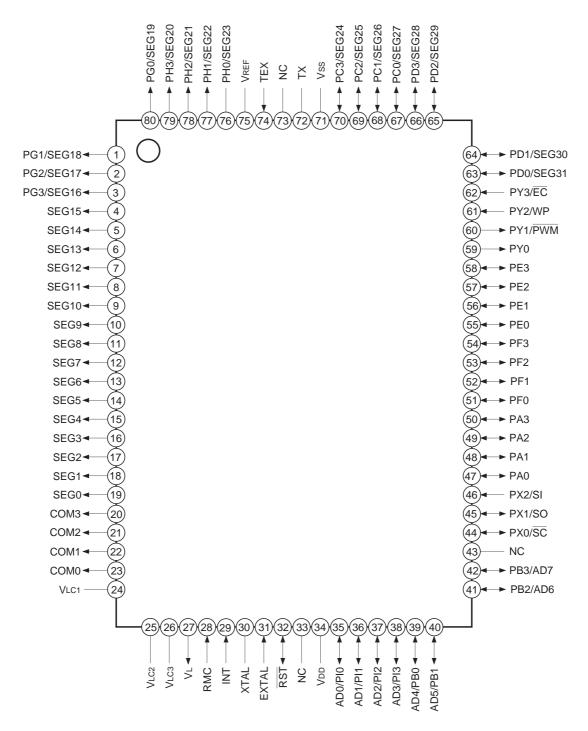

## Pin Configuration (Top View)

Note) Do not make any connections to NC pins.

## **Pin Description**

| Symbol | Name                     | I/O | Equivalent Circuit                                                                                                                                            | Description                                                                                                                                                                                                                                                 |

|--------|--------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd    | Supply voltage           | —   |                                                                                                                                                               | Positive voltage supply pin                                                                                                                                                                                                                                 |

| Vss    | Grounding voltage        | _   |                                                                                                                                                               | GND pin                                                                                                                                                                                                                                                     |

| EXTAL  | Clock input              | I   | EXTAL O                                                                                                                                                       | Clock oscillation circuit input pin.<br>Connect the crystal oscillator or<br>ceramic resonator between the EXTAL<br>and XTAL. When using as the<br>external clock input, connect the clock<br>oscillation source to the EXTAL pin<br>and open the XTAL pin. |

| XTAL   | Clock output             | 0   |                                                                                                                                                               | Clock oscillation circuit output pin                                                                                                                                                                                                                        |

| RST    | Reset                    | I/O | Mask option (E)<br>Mask option (E)<br>N<br>Mask option (E)<br>N<br>N<br>N-ch Tr output<br>Schmitt inverter input                                              | Serves as the incorporated power-on<br>reset circuit output pin.<br>When inputting a reset signal from the<br>outside, provide 2 instruction cycles or<br>longer of an "L" level (0V).                                                                      |

| INT    | External interrupt       | I   | ·                                                                                                                                                             | Serves the interrupt input pin.<br>Permits the selection with a program<br>of the edge and the level modes.                                                                                                                                                 |

| RMC    | Remote control input     | I   | Schmitt inverter input                                                                                                                                        | Remote control receiver input pin                                                                                                                                                                                                                           |

| PX2/SI | Port X2<br>Serial input  | I   |                                                                                                                                                               | Doubles as a serial interface (8 bits) input pin and as bit "2" (input) of port X.                                                                                                                                                                          |

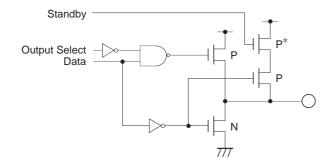

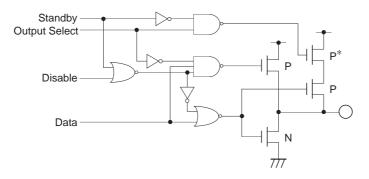

| PX1/SO | Port X1<br>Serial output | I/O | Data<br>Output Select<br>Disable<br>Standby<br>(Only during<br>tri-state output)<br>N<br>H<br>See Note 2) for the output<br>circuit format.<br>Inverter input | Doubles as a serial interface (8 bits)<br>output pin and as bit "1" (input) of<br>port X. (SO output possible to inhibit<br>with the program.)                                                                                                              |

| Symbol                   | Name                                  | I/O | Equivalent Circuit                                                                                                                                          | Description                                                                                                                                                                                                                                                               |

|--------------------------|---------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PX0/SC                   | Port X0<br>Serial clock               | I/O | Data<br>Output Select<br>Disable<br>Standby<br>(Only during<br>tri-state output)<br>See Note 2) for the output<br>circuit format.<br>Schmitt inverter input | Doubles as shift clock input/output pin<br>for the serial interface and as bit "0"<br>(input) of port X.                                                                                                                                                                  |

| PY3/EC                   | Port Y3<br>Event count<br>input       | I   | ◦ <b>」</b>                                                                                                                                                  | Doubles as event counter (8 bits) input pin and as bit "3" (input) of port Y.                                                                                                                                                                                             |

| PY2/WP                   | Port Y2<br>Wake-up<br>input           | I   | Schmitt inverter input                                                                                                                                      | Doubles as wake-up input pin to<br>release the standby state and as bit<br>"2" (input) of port Y.                                                                                                                                                                         |

| PY1/PWM                  | Port Y1<br>PWM<br>generator<br>output | ο   | Data                                                                                                                                                        | Doubles as PWM generator (14 bits)<br>output pin and as bit "1" (output) of<br>port Y.                                                                                                                                                                                    |

| PY0                      | Port Y0                               | 0   | circuit format.                                                                                                                                             | Output pin for bit "0" of port Y.                                                                                                                                                                                                                                         |

| PA0<br>to<br>PA3         | Port A                                | I/O | Data —<br>Output Select — (Note 2) — • – •                                                                                                                  | This 4-bit input/output port permits its<br>each individual bit to be programmed<br>to serve either as input or output. For<br>the output format, a tri-state and pull-<br>up resistor possible to be programmed,<br>and it is also used as the standby<br>resetting pin. |

| PB0/AD4<br>to<br>PB3/AD7 | Port B<br>Analog voltage<br>input     | I/O | Olisable (Note 2)<br>Standby (Only during<br>tri-state output)                                                                                              | This 4-bit input/output port has the functions that are equivalent to those of port A. It is also used for A/D converter input.                                                                                                                                           |

| PE0<br>to<br>PE3         | Port E                                | I/O | See Note 2) for the output                                                                                                                                  | This 4-bit input/output port permits its<br>each individual port to be programmed<br>to serve either as input or output. For<br>the output format, a tri-state and pull-<br>up resistor possible to be programmed.                                                        |

| PF0<br>to<br>PF3         | Port F                                | I/O | circuit format.<br>Inverter input                                                                                                                           | This 4-bit input/output port has the functions that are equivalent to those of port E.                                                                                                                                                                                    |

| PI0/AD0<br>to<br>PI3/AD3 | Port I<br>Analog voltage<br>input     | I/O |                                                                                                                                                             | This 4-bit input/output port has the functions that are equivalent to those of port E.<br>It is also used for A/D converter input.                                                                                                                                        |

| Symbol                               | Name                        | I/O | Equivalent Circuit                                                                            | Description                                                                                                                                                        |

|--------------------------------------|-----------------------------|-----|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD3/<br>SEG31<br>to<br>PD0/<br>SEG28 | Port D<br>Segment<br>output | Ο   | ⊥<br>Segment<br>PN ∽                                                                          | Doubles as a 4-bit output port (For the output format, the inverter and pull-up resistor possible to be programmed.) and as the segment signal output pin for LCD. |

| PC3/<br>SEG27<br>to<br>PC0/<br>SEG24 | Port C<br>Segment<br>output | Ο   | The transfer gate input signal<br>is controlled based on 1/2, 1/3<br>bias method in advance.  | Doubles as a 4-bit output port (The output format is equivalent to port D.) and as the segment signal output pin for LCD.                                          |

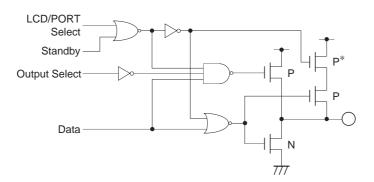

| PH3/<br>SEG23<br>to<br>PH0/<br>SEG20 | Port H<br>Segment<br>output | 0   | Data<br>Output Select<br>Standby<br>LCD/PORT<br>select                                        | Doubles as a 4-bit output port (The output format is equivalent to port D.) and as the segment signal output pin for LCD. (Possible to designate in bit units.)    |

| PG3/<br>SEG19<br>to<br>PG0/<br>SEG16 | Port G<br>Segment<br>output | 0   | See Note 3) for the output circuit format.                                                    | Doubles as a 4-bit output port (The output format is equivalent to port D.) and as the segment signal output pin for LCD.                                          |

| SEG0<br>to<br>SEG15                  | Segment<br>output           | 0   | The transfer gate input signal<br>is controlled based on 1/2, 1/3<br>bias methods in advance. | Segment signal output pin for LCD                                                                                                                                  |

| COM0<br>to<br>COM3                   | Common<br>output            | 0   | Transfer gate output                                                                          | Common signal output pin for LCD                                                                                                                                   |

| VLC1<br>to<br>VLC3                   | Power supply for LCD        | _   |                                                                                               | Bias power supply pin for LCD                                                                                                                                      |

| VL                                   | Cut-off<br>output           | 0   | °───<br>N                                                                                     | Control pin which cuts off the current input to the bias resistor for the external LCD during standby.                                                             |

| Symbol | Name                      | I/O | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                   |

|--------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP     | Wake-up<br>input          | I   | Schmitt inverter input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | It is the input pin to release the standby mode, and release by "1".                                                                                                                                                                          |

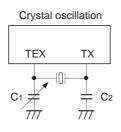

| тех    | 32kHz T/C<br>clock input  | I   | TEX OF ICAL DATE O | Input pin for 32kHz timer clock<br>generation circuit. Connect the<br>32.768kHz crystal oscillator between<br>TEX and TX. When using as the<br>event clock input, connect the clock<br>oscillation source to the TEX pin,<br>open the TX pin. |

| тх     | 32kHz T/C<br>clock output | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output of clock generation circuit                                                                                                                                                                                                            |

| Vref   | Reference voltage input   | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reference voltage input for power<br>supply voltage resetting circuit.<br>Connect the zener diode normally.                                                                                                                                   |

For all output ports, the output states of ports during standby possible to be programmed to the state holding before standby or the change to the high impedance.

When the pull-up resistor output is selected, it becomes a pulled-up state even it is input port.

During standby, it is impossible to change to the high impedance of PY0 and PY1 in the inverter output state. To change to the high impedance, select the pull-up resistor output, and then set to the high level output ("1" state).

Note 1) Possible to select out of the following two ways for the output circuit format.

(port units: programmable)

- (a) Inverter output

- (b) Pull-up resistor output

- **Note 2)** Possible to select out of the following two ways for the output circuit format. (port units: programmable)

- (a) Tri-state output

- (b) Pull-up resistor output

- **Note 3)** Possible to select out of the following two ways for the output circuit format. (port units: programmable)

- (a) Inverter output

- (b) Pull-up resistor output

\* As the output pull-up resistor is CMOS pull-up output of about 10kΩ, the pull-up resistor becomes OFF state during "L" output.

(Vss = 0V)

## **Absolute Maximum Ratings**

$(Ta = -20 \text{ to } +75^{\circ}\text{C}, \text{Vss} = 0\text{V})$

| Item                            | Symbol                 | Rating                     | Unit | Remarks                         |

|---------------------------------|------------------------|----------------------------|------|---------------------------------|

| Power supply voltage            | Vdd                    | -0.3 to +7.0               | V    |                                 |

| LCD bias voltage                | Vcl1,<br>Vcl2,<br>Vcl3 | -0.3 to +7.0 <sup>*1</sup> | V    |                                 |

| Input voltage                   | Vin                    | -0.3 to +7.0 <sup>*1</sup> | V    |                                 |

| Output voltage                  | Vouт                   | -0.3 to +7.0 <sup>*1</sup> | V    |                                 |

| High level output current       | Іон                    | -5                         | mA   | General purpose port*2: per pin |

| High level total output current | ∑Іон                   | -50                        | mA   | Entire pins total               |

|                                 | lol                    | 15                         | mA   | General purpose port*2: per pin |

| Low level output current        | lorc                   | 20                         | mA   | High current port*3: per pin    |

| Low level total output current  | ΣΙοι                   | 100                        | mA   | Entire pins total               |

| Operating temperature           | Topr                   | -20 to +75                 | °C   |                                 |

| Storage tamperature             | Tstg                   | -55 to +150                | °C   |                                 |

| Allowable power dissipation     | PD                     | 600                        | mW   |                                 |

\*1 VLC1, VLC2, VLC3, VIN and VOUT should not exceed VDD + 0.3V.

\*2 Specifies the output current of the general purpose I/O port PA to PI, SO,  $\overline{SC}$ , PY0 and PY1.

<sup>\*3</sup> The high current operation transistors are the N-ch transistors of the PC and PD ports.

**Note)** Usage exceeding absolute maximum ratings may permanently impair the LSI. Normal operation should better take place under the recommended operation conditions. Exceeding those conditions may adversely affect the reliability of the LSI.

## **Recommended Operating Condition**

Unit Remarks Item Symbol Min. Max. Guaranteed range of operation by V 4.5 5.5 EXTAL clock Guaranteed range of operation by Power supply voltage Vdd 2.5 5.5 V TEX clock, guaranteed range of data hold during STOP. VCL1, VCL2, Vdd V LCD bias voltage Vss Liquid crystal power supply range\*1 Vcl 3 Vін 0.7Vdd Vdd V Vdd V Hysteresis input\*2 High level input voltage VIHS 0.8VDD EXTAL pin\*3 VIHEX Vdd - 0.4 VDD + 0.3 V 0.3Vdd V VIL 0 0.2Vdd V 0 Hysteresis input\*2 Low level input voltage VILS VILEX -0.30.4 V EXTAL pin\*3 -20 +75 °C Operating temperature Topr

\*1 The optimum value is determined by the characteristics of the liquid crystal display element used.

\*2 The TEX pin when the counter mode is selected by each of INT, RMC, PX0, PX2, PY2, PY3, RST pins and mask option.

\*3 Specified only during external clock input.

## **Electrical Characteristics**

## **DC** characteristics

| $(Ta = -20 \text{ to } +75^{\circ}C, \text{ Vss})$ | = 0V) |

|----------------------------------------------------|-------|

|----------------------------------------------------|-------|

| ltem                                     | Symbol | Pin                                                                                                                                                                                                                                                                          | Condition                                                                           | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

|                                          |        |                                                                                                                                                                                                                                                                              | Vdd = 4.5V, Iон = -0.5mA* <sup>2</sup>                                              | 4.0  |      |      | V    |

| High level                               |        |                                                                                                                                                                                                                                                                              | VDD = 4.5V, Iон = -1.0mA*2                                                          |      |      |      | V    |

| High level<br>output voltage             | Vон    | PA to PI <sup>*1</sup><br>PX0, PX1                                                                                                                                                                                                                                           | Vdd = $4.5V$ , Ioh = $-10\mu A^{*3}$                                                | 4.0  |      |      | V    |

|                                          |        | PY0, PY1                                                                                                                                                                                                                                                                     | $V_{DD} = 4.5V$ , IOH = $-200\mu A^{*3}$                                            | 2.4  |      |      | V    |

|                                          |        | <u>VL (</u> Vo∟ only)<br>RST (Vo∟ only)                                                                                                                                                                                                                                      | VDD = 4.5V, IOL = 1.8mA                                                             |      |      | 0.4  | V    |

| Low level VoL                            | Vol    | PC*1, PD*1                                                                                                                                                                                                                                                                   | VDD = 4.5V, IOL = 3.6mA                                                             |      |      | 0.6  | V    |

|                                          |        |                                                                                                                                                                                                                                                                              | VDD = 4.5V, IOL = 12mA                                                              |      |      | 1.5  | V    |

|                                          | Ііне   | EXTAL                                                                                                                                                                                                                                                                        | Vdd = 5.5V, Vih = 5.5V                                                              | 0.5  |      | 40   | μA   |

|                                          | IILE   | EXTAL                                                                                                                                                                                                                                                                        | $V_{DD} = 5.5V, V_{IL} = 0.4V$                                                      | -0.5 |      | -40  | μA   |

|                                          | Інт    | TEX*4                                                                                                                                                                                                                                                                        | Vdd = 5.5V, Vih = 5.5V                                                              | 0.1  |      | 10   | μA   |

| Input current                            | lilt   |                                                                                                                                                                                                                                                                              |                                                                                     | -0.1 |      | -10  | μA   |

|                                          | lilr   | RST*⁵                                                                                                                                                                                                                                                                        | $V_{DD} = 5.5V, V_{IL} = 0.4V$                                                      | -1.5 |      | -400 | μA   |

|                                          | lı∟    | PA*6, PB*6, PE*6,                                                                                                                                                                                                                                                            |                                                                                     |      |      | ±10  | μA   |

| High impedance<br>I/O leakage<br>current | lız    | PF <sup>*6</sup> , PI <sup>*6</sup> , PX0 <sup>*6</sup> ,<br>PX1 <sup>*6</sup> , PX2 <sup>*8</sup> , PY0 <sup>*7</sup> ,<br>PY1 <sup>*7</sup> , PY2 <sup>*8</sup> , PY3 <sup>*8</sup> ,<br><u>INT<sup>*8</sup>, RMC<sup>*8</sup>,<br/>RST<sup>*5</sup>, TEX<sup>*4</sup></u> | VDD = 5.5V, VI = 0, 5.5V                                                            |      |      | ±10  | μA   |

| Common output impedance                  | Rсом   | COM0 to COM3                                                                                                                                                                                                                                                                 | VDD = 5V<br>VLC1 = 3.75V                                                            |      | 3    | 5    | kΩ   |

| Segment output<br>impedance              | Rseg   | SEG0 to SEG15<br>SEG16 to SEG31 <sup>*1</sup>                                                                                                                                                                                                                                | VLC2 = 2.5V<br>VLC3 = 1.25V                                                         |      | 5    | 15   | kΩ   |

|                                          |        |                                                                                                                                                                                                                                                                              | Entire output pins open                                                             |      |      |      |      |

|                                          | Idd1   |                                                                                                                                                                                                                                                                              | Crystal oscillation<br>(C1 = C2 = 22pF)<br>of VDD = 5.5V, 4.19MHz                   |      | 7    | 20   | mA   |

|                                          | Idd2   |                                                                                                                                                                                                                                                                              | Crystal oscillation<br>(C1 = C2 = $47pF$ )<br>of VDD = 3V, 32kHz                    |      | 50   | 250  | μA   |

|                                          |        |                                                                                                                                                                                                                                                                              | Sleep mode                                                                          |      |      |      |      |

| Supply current                           | IDDSP1 | Vdd                                                                                                                                                                                                                                                                          | V <sub>DD</sub> = 5.5V,<br>4.19MHz oscillation                                      |      | 5    | 12   | mA   |

|                                          | DDSP2  |                                                                                                                                                                                                                                                                              | VDD = 3V, 32kHz oscillation                                                         |      | 40   | 200  | μA   |

|                                          | DDS1   |                                                                                                                                                                                                                                                                              | Stop mode                                                                           |      | 7    | 40   | μA   |

|                                          | IDD31  |                                                                                                                                                                                                                                                                              | $V_{DD} = 3V, 32kHz$ with T/C                                                       |      | '    | 40   | μΛ   |

|                                          | IDDS2  |                                                                                                                                                                                                                                                                              | VDD = 5.5V, 32kHz without T/C<br>(For mask option select<br>counter, Pin is fixed.) |      |      | 10   | μA   |

| Input capacity                           | Cin    | Other than VLC1 to<br>VLC3, COM0 to COM3,<br>SEG0 to SEG15,<br>SEG16 to SEG31*1,<br>Vss, VDD pins                                                                                                                                                                            | Clock 1MHz<br>0V other than the measured pins                                       |      | 10   | 20   | pF   |

- \*1 The PC, PD, PG and PH show when the combined pins are selected as the port, and SEG16 to SEG31 show when the combined pins are selected as the segment output.

- \*2 It is when the respective pins of PA to PI, PX0 and PX1 select the tri-state output circuit, and PY0 and PY1 are when the inverter output circuit is selected.

- \*3 It is when the respective pins of PA to PI, PX0, PX1, PY0 and PY1 select the pull-up resistor.

- \*4 The TEX pin specifies the input current when the crystal oscillation is selected by the mask option, and specifies the leakage current when the schmitt input is selected.

- \*5 The RST pin specifies the input current when the pull-up resistor is selected, and specifies leakage current when non-resistor is selected.

- \*6 The respective pins of PA, PB, PE, PF, PI, PX0 and PX1 specify the input current when the pull-up resistor is selected, and specify the leakage current when the port state during using the tri-state output circuit or standby is selected at high impedance.

- \*7 The respective pins of PY0 and PY1 specify the input current when the pull-up resistor is selected, and specify the leakage current when the port state during standby is selected at high impedance.

- \*8 The respective pins of PX2, PY2, PY3, INT and RMC only specify the leakage current.

## AC characteristics

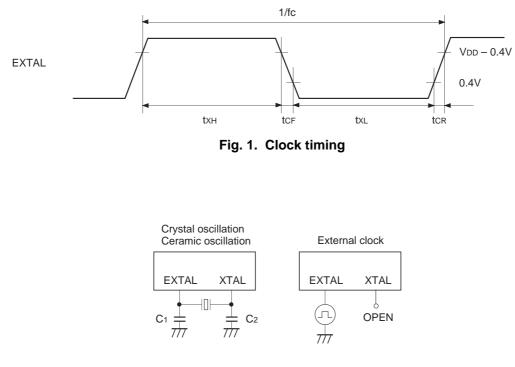

(1) Clock timing

$(Ta = -20 \text{ to } +75^{\circ}C, V_{DD} = 4.5 \text{ to } 5.5V, V_{SS} = 0V)$

| Item                                             | Symbol     | Pin           | Condition                               | Min.                         | Тур.   | Max. | Unit |

|--------------------------------------------------|------------|---------------|-----------------------------------------|------------------------------|--------|------|------|

| System clock frequency                           | fc         | XTAL<br>EXTAL | Fig. 1, Fig. 2                          | 1                            |        | 5    | MHz  |

| System clock input pulse width                   | tx∟<br>txн | EXTAL         | Fig. 1, Fig. 2                          | 90                           |        |      | ns   |

| System clock input rising and falling times      | tcr<br>tcr | EATAL         | (External clock drive)                  |                              |        | 200  | ns   |

| System clock frequency                           | fcs        | TEX*2<br>TX   | V <sub>DD</sub> = 2.5 to 5.5V<br>Fig. 3 |                              | 32.768 |      | kHz  |

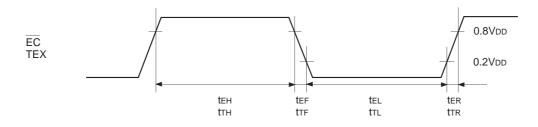

| Event count clock input pulse width              | tel<br>teн | ĒĊ            | Fig. 4                                  | tsys <sup>*1</sup><br>+ 0.05 |        |      | μs   |

| Event count clock input rising and falling times | ter<br>ter | ĒĊ            | Fig. 4                                  |                              |        | 20   | ms   |

| Event count input clock input pulse width        | tт∟<br>tтн | TEX*3         | Fig. 4                                  | 10                           |        |      | μs   |

| Event count input clock rising and falling times | ttr<br>ttf | TEX*3         | Fig. 4                                  |                              |        | 20   | ms   |

\*1 tsys in the EXTAL input clock is 8/fc.

tsys in the TEX input clock is 4/fcs.

\*2 Specified when the crystal oscillation mode is selected by the mask option.

\*3 Specified when the counter mode is selected by the mask option.

Note) When adjusting the frequency accurately, there may be cases in which they may differ from Fig. 2.

Fig. 2. Clock applying condition

Fig. 3. 32kHz clock applying condition

Fig. 4. Event count clock timing

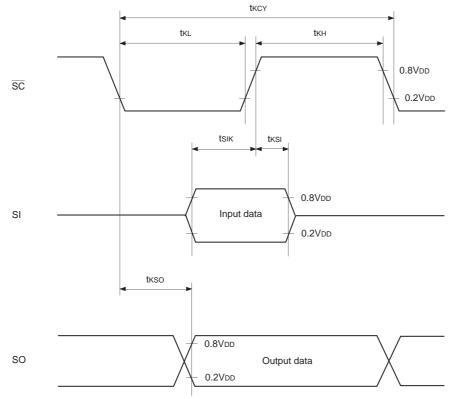

## (2) Serial transfer

$(Ta = -20 \text{ to } +75^{\circ}\text{C}, \text{V}_{DD} = 4.5 \text{ to } 5.5\text{V}, \text{V}_{SS} = 0\text{V})$

| Item                                                              | Symbol     | Pin | Condition      | Min.          | Max.         | Unit |

|-------------------------------------------------------------------|------------|-----|----------------|---------------|--------------|------|

| Serial transfer clock ( $\overline{SC}$ )                         | tĸcy       | SC  | Input mode     | tsys/4 + 1.42 |              | μs   |

| cycle time                                                        |            |     | Output mode    | 2tsys         |              | μs   |

|                                                                   |            |     | Input mode     | tsys/8 + 0.7  |              | μs   |

| Serial transfer clock (SC)<br>high and low level widths           | tĸн<br>tĸ∟ | SC  | Output mode*1  | tsys – 0.1    |              | μs   |

|                                                                   |            |     | Output mode*2  | tsys – 1.6    |              | μs   |

| Serial data input setup                                           | tsıк       | SI  | SC input mode  | 0.1           |              | μs   |

| time (against SC ↑)                                               |            |     | SC output mode | 0.2           |              | μs   |

| Serial data input hold                                            | tĸsi       | SI  | SC input mode  | tsys/8 + 0.5  |              | μs   |

| time (against SC ↑)                                               |            |     | SC output mode | 0.1           |              | μs   |

| High data <u>out</u> put delay time from SC falling <sup>*3</sup> | tĸso       | SO  |                |               | tsys/8 + 0.5 | μs   |

| High data output delay time from SC falling*4                     | tĸso       | SO  |                |               | tsys/8 + 1.6 | μs   |

| Low data <u>out</u> put delay time from SC falling                | tĸso       | SO  |                |               | tsys/8 + 0.5 | μs   |

Notes) 1. tsys in the EXTAL input clock is 8/fc. (It is impossible to use in TEX input clock.) 2. The load of data output delay is 50pF + 1TTL.

\*1 It is specified when  $PX0/\underline{SC}$  pin is selected to the tri-state output by the program.

\*2 It is specified when PX0/SC pin is selected to the pull-up resistance by the program. As the tsys receives restriction by this item, take notice that it limits the upper limit of the system clock frequency fc.

\*3 This item is specified when PX1/SO pin is selected to the tri-state output by the program.

\*4 This item is specified when PX1/SO pin is selected to the pull-up resistance by the program.

– 13 –

## (3) A/D converter

$(Ta = -20 \text{ to } +75^{\circ}\text{C}, \text{ Vss} = 0\text{V})$

| Analog input voltage | Pin              | Condition | Digital conversion value |

|----------------------|------------------|-----------|--------------------------|

| 0.0 to 0.33V         | AD0<br>to<br>AD7 |           | 000                      |

| 0.82 to 1.29V        |                  | Vdd = 5V  | 001                      |

| 1.78 to 2.21V        |                  |           | 010                      |

| 2.69 to 3.06V        |                  |           | 011                      |

| 3.56 to 4.06V        |                  |           | 100                      |

| 4.62 to 5.0V         |                  |           | 101                      |

Note) The digital conversion value are the values when ABH address of the RAM file 1 in the program are read.

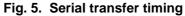

(4) Power Supply Voltage Detection Reset Function

$(Ta = -20 \text{ to } + 75^{\circ}\text{C}, \text{ Vss} = 0\text{V})$

| Item                                                                           | Symbol | Pin | Condition                                                                                       | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------|--------|-----|-------------------------------------------------------------------------------------------------|------|------|------|------|

| Power supply voltage<br>detection reset function of<br>operation voltage range | Vlpop  | Vdd | Voltage range allowing system<br>operation (32kHz system<br>operation below VDD = 4.5V)         | 2.5  |      | 5.5  | V    |

| Power supply voltage drop detection function                                   | Vpop   | Vdd | When VREF pin voltage is 3.3V<br>Flag set when voltage drops<br>System reset when voltage rises | 3.8  | 4.0  | 4.2  | V    |

The graph in Fig. 6 shows the relationship between the power supply voltage VDD and reference voltage VREF of the power supply voltage detection reset function.

**Note)** The graph in Fig. 6 serves as guide to the function operation area obtained using average devices. Individual adjustment is needed when Zener diodes, etc., are connected to the VREF pin.

Fig. 6. Power supply voltage detection reset function chart

## (5) Others

$(Ta = -20 \text{ to } +75^{\circ}\text{C}, \text{V}_{DD} = 4.5 \text{ to } 5.5\text{V}, \text{V}_{SS} = 0\text{V})$

| Item                                            | Symbol     | Pin           | Condition                     | Min.        | Max. | Unit |

|-------------------------------------------------|------------|---------------|-------------------------------|-------------|------|------|

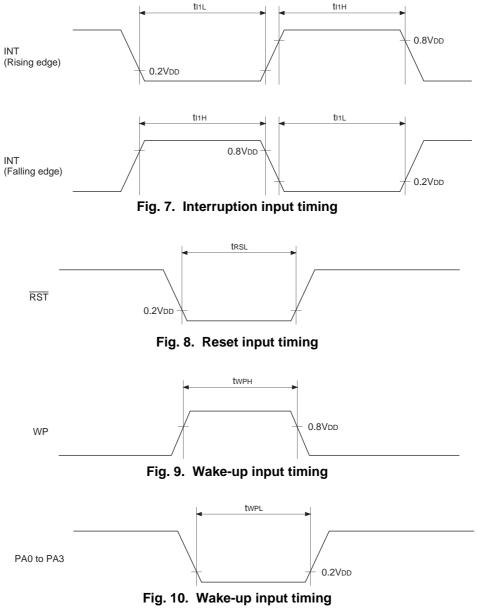

| External interruption high and low level widths | tııн, tıı∟ | INT           | During edge<br>detection mode | tsys + 0.05 |      | μs   |

| Reset input low level width                     | trsl       | RST           |                               | 2tsys*1     |      | μs   |

| Wake up input high lovel width                  | twpн       | WP            | Stop mode                     | 500         |      | ns   |

| Wake-up input high level width                  |            |               | Sleep mode                    | tsys + 0.05 |      | μs   |

| Make up input low lovel width                   | twpL       | PA0 to<br>PA3 | Stop mode                     | 500         |      | ns   |

| Wake-up input low level width                   |            |               | Sleep mode                    | tsys + 0.05 |      | μs   |

Note) tsys in the EXTAL input clock is 8/fc.

tsys in the TEX input clock is 4/fcs.

\*1 For resetting when operating in TEX input clock, hold the low level more than the oscillation stabilizing time of EXTAL input clock.

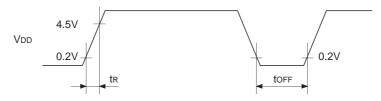

## Power on reset\*

$(Ta = -20 \text{ to } +75^{\circ}\text{C}, \text{ Vss} = 0\text{V})$

| Item                      | Symbol | Pin | Condition                 | Min. | Max. | Unit |

|---------------------------|--------|-----|---------------------------|------|------|------|

| Power supply rising time  | tR     | Vdd | Power on reset            | 0.05 | 50   | ms   |

| Power supply cut-off time | toff   |     | Repetitive power on reset | 1    |      | ms   |

\* Specifies only when power on reset function is selected.

The power supply should rise smoothly.

Fig. 11. Power on reset

### **Notes on Application**

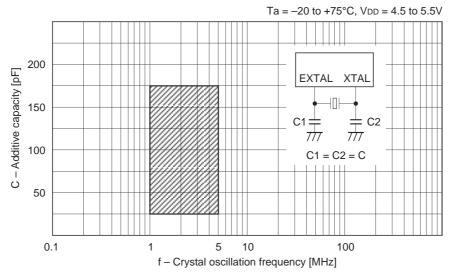

See Fig. 11, Additive capacity calculation chart, when using the crystal oscillator and select the appropriate capacity.

Fig. 12. Crystal oscillation circuit additive capacity calculation chart

**Note)** The above chart shows a range in which the average quartz resonator has a relatively fast oscillation rising edge and stable characteristics. The capacity should be selected to correspond to the appropriate constant for each quartz resonator, should the frequency of the quartz resonator be accurately adjusted.

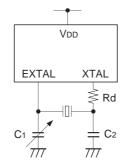

Fig. 13 shows an example of a circuit which can accurately adjust the frequency. Used here a trimmer capacitor.

Fig. 13. Frequency adjustment circuit

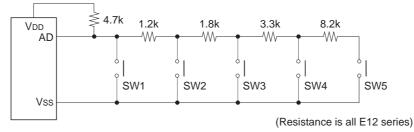

When using the A/D converter as the key input, it is recommended that the circuit structure shown in Fig. 14 be used.

Fig. 14. Recommended example of key circuit by A/D converter

Package Outline Unit: mm

```

DETAIL A

```

| SONY CODE  | QFP-80P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP080-P-1420 |

| JEDEC CODE |               |

## PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN     |  |

|------------------|-----------------|--|

| LEAD TREATMENT   | SOLDER PLATING  |  |

| LEAD MATERIAL    | 42/COPPER ALLOY |  |

| PACKAGE MASS     | 1.6g            |  |

## 80PIN QFP (PLASTIC)